【シリコン半導体の研磨技術】経済大国日本を支えた研磨技術を徹底解説

2026/02/12

2026/02/11

日本が「経済大国」と呼ばれた時代、その成長を足元で支えてきた技術の一つが研磨技術です。

一見すると地味に見える研磨ですが、実は日本のものづくりの競争力を根底から支えてきた、極めて重要な要素技術です。

自動車、工作機械、光学部品、精密金型等々。

これらの分野で日本製品が高い信頼を獲得できた背景には、「削れる」「磨ける」「狙った面が出せる」という現場力がありました。

ミクロン、サブミクロンという世界で品質を作り込む研磨技術は、日本の製造業そのものと言っても過言ではありません。

そして現在、その研磨技術の価値が半導体分野で改めて注目されています。

シリコンウエハはもちろん、SiCやGaNといった次世代パワー半導体材料では、結晶の硬さや化学的安定性の高さから、研磨・CMPプロセスがデバイス性能を左右する非常に重要な工程です。

そこで、本ブログの新シリーズ、「経済大国日本を支えた研磨技術」の1回目として、「シリコン半導体の研磨技術」を取り上げることとします。

半導体産業の原点とも言えるシリコンウエハ。

その品質を確実に支えてきたのが研磨技術です。

本稿では、シリコンウエハ研磨がどのように進化してきたのかを、時代背景とともに振り返ってみたいと思います。

株式会社斉藤光学製作所技術顧問。専門が「研磨加工」と「微粒子分散」の技術コンサルタント。1976年、東北大学工学部を卒業後にタイホー工業株式会社 中央研究所にて磁性流体や研磨加工の研究に従事。1987年、東京大学より工学博士号(機械工学)を授与。2001年から3年間、東京大学生産技術研究所の客員教授。その後10年間は、研磨材メーカーの株式会社フジミインコーポレーテッド。さらにその後10年間は、国立研究開発法人 産業技術総合研究所 招聘研究員だった。

プロフィール詳細を見る半導体製造の重要性とは

半導体では「平坦であること」「ダメージがないこと」「再現性があること」が強く求められます。

これはまさに、長年日本の研磨現場が培ってきた知見、砥粒の選定、荷重と速度のバランス、表面状態の見極め等々。

こうした「暗黙知」が強みとして生きる世界です。

世界的に半導体製造の重要性が高まる中で、装置や材料に注目が集まりがちですが、最終的な品質を決めるのは「面を作る技術」となります。

研磨は決して裏方ではなく、これからの半導体産業を支える主役級の基盤技術と言えるでしょう。

日本が積み上げてきた研磨技術は、過去の遺産ではありません。

次世代半導体という新たな舞台で、再び世界を支える力になる。

その可能性は、今まさに現場にあるのではないでしょうか。

半導体黎明期におけるウエハ研磨

半導体デバイスの始まりは、1947年、アメリカのベル研究所でジョン・バーディーンと、ウォルター・ブラッテンという2人の科学者によって発明されたトランジスタです。

この発明は、真空管に代わる新しい増幅素子として開発されました。

小型・低消費電力・高耐久性を兼ね備え、電子機器を一気に小型化する画期的なものでした。

最初のトランジスタは「点接触型トランジスタ」と呼ばれ、ゲルマニウムの単結晶に2本の針を立てて電流を流すことで動作します。

半導体結晶の表面研磨の必要性は、1955年のゲルマニウム拡散型トランジスタの発明において重要性が認識されました。

しかし、その加工方法はダイヤモンドスラリーや酸化アルミニウムによる機械的(メカニカル)なポリシング法でした1)。

砥粒径をいかに小さくしても中々スクラッチが解消されず、加工変質層との戦いには長時間の加工が必要です。

コロイダルシリカを用いたCMP(Chemical Mechanical Polishing)が導入されたのは1965年頃で、シリコン単結晶を用いたデバイスの製造工程で使用されました1)。

高い研磨レートとスクラッチのない加工法の誕生は、当時、メカニカル加工後の加工変質層除去に行われていた、塩酸によるベーパーエッチング工程を省略することとなります。

その結果、ウエハ製造コスト削減に大きく貢献することとなりました。

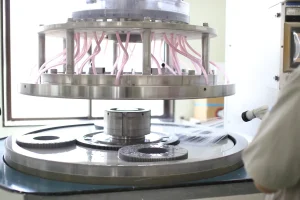

現在までこのCMP加工法は、使用される砥粒の種類やケミカル作用の化学薬品の組成は変わっても基本的な加工方法は1965年頃と変わっていません1) (図1) 。

CMPによる平滑な表面は、電子がデバイス内をスムーズに移動できるようにし、デバイスの性能を向上させます。

その後もコロイダルシリカは加工対象の広さや、使い勝手の良さ、材料の量産安定性やコストパフォーマンスの良さから広く普及しました。

この技術革新を民生市場に結びつけたのが、日本のソニー(当時・東京通信工業)です。

1955年に日本初のトランジスタラジオ「TR-55」を発売し、さらに1957年には米国市場向けに小型の「TR-63」を投入。

これが大ヒットとなり、トランジスタラジオは世界中に広まりました。

トランジスタラジオの大衆化は、ソニーを世界的なブランドに押し上げただけでなく、日本の研磨・加工技術の水準を世界レベルへと引き上げる契機でもあったのです。

シリコンウエハサイズ/回路線幅の変遷と研磨技術の進歩

ここで、シリコンウエハサイズ/回路線幅の変遷を図2に示します。

上段にウエハサイズ/回路線幅の変遷を、下段にそれに伴う研磨技術の役割・課題の進化を示しています。

半導体産業において、デバイスの高性能化は、回路線幅の微細化によって実現されてきました。

一方、シリコンウエハの大口径化は、生産性向上とコスト低減を実現するための重要な進化の軸です。

しかし、その裏側では、回路線幅の微細化とウエハサイズの拡大に伴い、研磨技術にも質的な進化が求められてきました。

図3には各年代の時代背景を代表する、半導体を使った大衆商品のイメージ図を示します。

IC黎明期【1960~1970年代】

1960年頃には半導体材料の主流はゲルマニウムからシリコンに取って代わられます。

高性能にも関わらず、より硬く脆い材料であることにより、最終ポリシングにおける加工変質層の解消が重要性を増してきました。

IC黎明期では、ウエハは未だ小径であり、回路線幅も比較的粗く、研磨に求められる主目的はスライスで入ったダメージの除去、デバイス形成に十分な鏡面の創生でした。

1960年代後半から1970年代にかけて、半導体産業は「トランジスタの時代」から「IC(集積回路)の時代」へと大きくシフトしました。

その原動力の一つが、日本発の電子式卓上電卓です。

1964年にシャープが世界初のトランジスタ式電卓を発売。

その後、IC化が進むと、電卓は小型化・低価格化し、瞬く間に普及しました。

ここで使われたのがシリコンICであり、より高品質なシリコンウエハが求められるようになります。

IC時代になると、単なる「平坦な基板」では不十分で、以下の要求が強まりました。

まず、フォトリソグラフィ精度を確保するために、ウエハ表面は従来以上に鏡面でなければなりませんでした。

また、電卓やコンピュータ需要に応えるために、ウエハは2インチから3インチ、さらに4インチへと拡大しました。

これに伴い、スライス・ラッピング・ポリッシング装置もスケールアップが必要となり、国産装置メーカーの技術開発が加速しました。

この技術の進化が、1980年代以降のLSI・VLSI時代、そして今日の先端半導体製造へとつながっていったのです。

LSI量産の本格化【1980年代】

1970年代にはLSI(大規模集積回路) 、1980年代にはVLSI(超大規模集積回路)が登場し、半導体チップ上に数万~数百万個のトランジスタが集積される時代へ突入しました。

LSIの進化により、パソコンとゲーム機が家庭に広がります。

NEC「PC-9800シリーズ」や任天堂「ファミリーコンピュータ」が象徴的です。

半導体メモリ、マイクロプロセッサが大衆化を後押しすることになるのです。

LSIの高集積化が進み、歩留まりが製造コストを左右する時代に入ると、研磨工程の役割は大きく変化します。

以下の重要な課題により、研磨の均一性への要求が顕在化しました。

- ウエハ面内の厚み均一性(TTV)の改善

- マイクロスクラッチ低減

- パーティクル管理の高度化

TTV(Total Thickness Variation)とは、ウエハ全体の厚みばらつきで、この頃には10µm→5µm 程度が求められました。

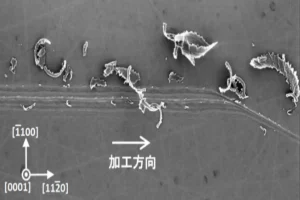

マイクロスクラッチとは、シリコンウエハ表面に形成される微細な線状欠陥です。

肉眼では認識できないものの、デバイス歩留まり・信頼性に重大な影響を与える研磨起因の欠陥のことを指します。

ここで言うパーティクルとは、砥粒凝集物(スラリー由来)や破砕したパッド片などを称し、マイクロスクラッチの原因ともなるのです。

DRAMやマイクロプロセッサの普及とともに、半導体は「数」だけでなく「性能」が問われる時代に入ります。

ウエハは4~6インチへと大口径化し、研磨工程にも面内均一性や反りの低減といった要求が加わりました。

この進化の裏側には、ウエハの加工・研磨技術の飛躍的な向上が不可欠でした。

なぜなら、回路線幅が微細化するほど、ウエハ表面の凹凸や微小欠陥がデバイス歩留まりに直結したからです。

日本はこの時期、いくつかの強みを武器に国際競争力を築いていきます。

- 超精密ラッピング・ポリッシング技術の確立

- 量産プロセス対応の設備増強

- 品質管理と現場力の強さ

その結果、1980年代から1990年代にかけて、日本の半導体材料・加工装置メーカーは世界市場で圧倒的なシェアを占めることになりました。

例えば、ウエハ研磨やCMP用スラリー、研磨パッドなどの分野では、現在に至るまで日本企業がトップを走り続けています。

つまり、LSI・VLSI時代は「精密加工=国際競争力」となった時代であり、日本の研磨技術が単なる裏方から「世界をリードする主役技術」へと飛躍した時代だったのです。

多層配線構造【1990年代】

1990年代はDRAM、フラッシュメモリの進化により、携帯電話やデジタルカメラが普及していきました。

液晶ディスプレイと合わせて「持ち歩く半導体製品」が一般化します。

半導体デバイスは線幅0.5µm以下の微細化が本格化し、LSIからVLSIへと急速に進化しました。

VLSIデバイスの高性能化は、トランジスタの高集積化によって達成されてきたのです。

しかし、限られた面積で高集積化を図るためには、基本素子の微細化とともに、配線の多層化が必要となってきました2)。

多層配線技術で不可欠となるのが、リソグラフィの焦点深度を確保するための平坦化処理です。

多層配線構造では、以下の問題が顕在化しました。

- 下層配線の段差が上層へ累積

- フォトリソグラフィの焦点ズレ

- 配線断線やショートの増加

従来のラッピングやポリシングは、ウエハ全体を一様に研磨する技術であり、こうした複雑な段差構造には対応できなくなっていたのです。

ここで登場したのが、プラナリゼーションCMP(Planarization-Chemical Mechanical Polishing)です。

これまで、ベアシリコンウエハの加工に限られていたCMP技術を、平坦化を目的に積極的に導入したことでVLSIデバイスの性能は格段に向上しました2)。

CMPは、化学反応による材料表面の軟化、パッドと砥粒による機械的除去を組み合わせることで、トポグラフィを選択的に平坦化できる研磨技術です。

これにより、層間絶縁膜(SiO₂)の高精度平坦化、タングステン埋め込み配線(Wプラグ)後の銅(Cu)配線プロセスが実用化され、多層配線LSIの量産が可能になりました2)。

CMPの導入によって、研磨は「最終仕上げ工程」から「デバイス性能を決める中核プロセス」へと位置づけが変わります。

研磨条件ひとつで、配線抵抗、寄生容量、歩留まりが左右されるようになり、研磨は設計・プロセス開発と直結する技術になりました。

大口径ウエハ対応【2000年代】

高性能CPUとNANDフラッシュの進化で登場するのがスマートフォンです。

iPhone(2007年)が社会を変え、半導体が「生活インフラ」になります。

ウエハ径は、デジタル社会の拡大とともに12インチが主流となります。

以下のような、nmオーダーの面内均一性が指標になりました。

- ナノトポグラフィ

- マイクロラフネス

- 表面欠陥密度

半導体デバイスは0.18µm世代から90nm、65nmへと急速に微細化が進み、配線多層化・Low-k材料の導入も本格化します。

研磨はもはや単独の工程ではなく、洗浄・計測・プロセス制御と一体化した総合技術へと進化しました。

それでも最終的な面品質を決めるのは、材料選定(砥粒、パッド)、加工条件(荷重、速度)など、現場で培われた研磨の知恵なのです。

3Dデバイス構造 【2010年代~現在】

2010年代以降、GPUやAIチップが普及し、クラウドサービス・スマート家電が当たり前になりました。

自動車もEV化・ADAS(自動運転支援)で半導体搭載量が急増します。

半導体は「大衆商品」から「社会インフラ」へと位置づけが変化しました。

デバイスは22nm世代以降、3Dデバイス構造「FinFET、3D NAND、GAA(Gate-All-Around) 」へと進化します。

そして、研磨技術にはナノスケールの形状制御と材料選択性を両立する高度なプロセス設計力が求められるようになったのです。

従来のCMPは、主として段差除去と平坦化(Planarization)が目的でした。

しかし2010年代以降は、以下のような、より複雑で三次元的な制御が重要視されるようになったのです2)。

- 局所形状(エッジロールオフ、パターン依存性)

- 膜種ごとの除去選択比

- ナノトポグラフィ(Nanotopography)

ウエハサイズが成熟期に入った一方で、研磨に要求される精度と知見は、今なお進化を続けているのが現状です。

おわりに

シリコンウエハの大口径化と回路線幅の微細化は、常に研磨技術の進歩と並走してきました。

研磨は決して「前工程の裏方」ではなく、デバイス性能と量産性を両立させる基盤技術です。

次世代半導体においても、その重要性はさらに高まっていくでしょう。

参考文献

1)I. Koshiyama:Research and Development on the Processing Methods of Substrate Surfaces for Electronics and the Consumable Materials, Doctoral Dissertation of I.Koshiyama, Japan (2006).

2)黒河周平:半導体プラナリゼーションCMP技術の展望,精密工学会誌 84 (3), (2018)213.